CV Input Signal Types #18 — Clock Division CV

| Property | Value |

|---|---|

| Category | Special |

| Voltage Range | 0..+5V |

| Polarity | Unipolar |

| Bandwidth | DC (stepped) |

Description

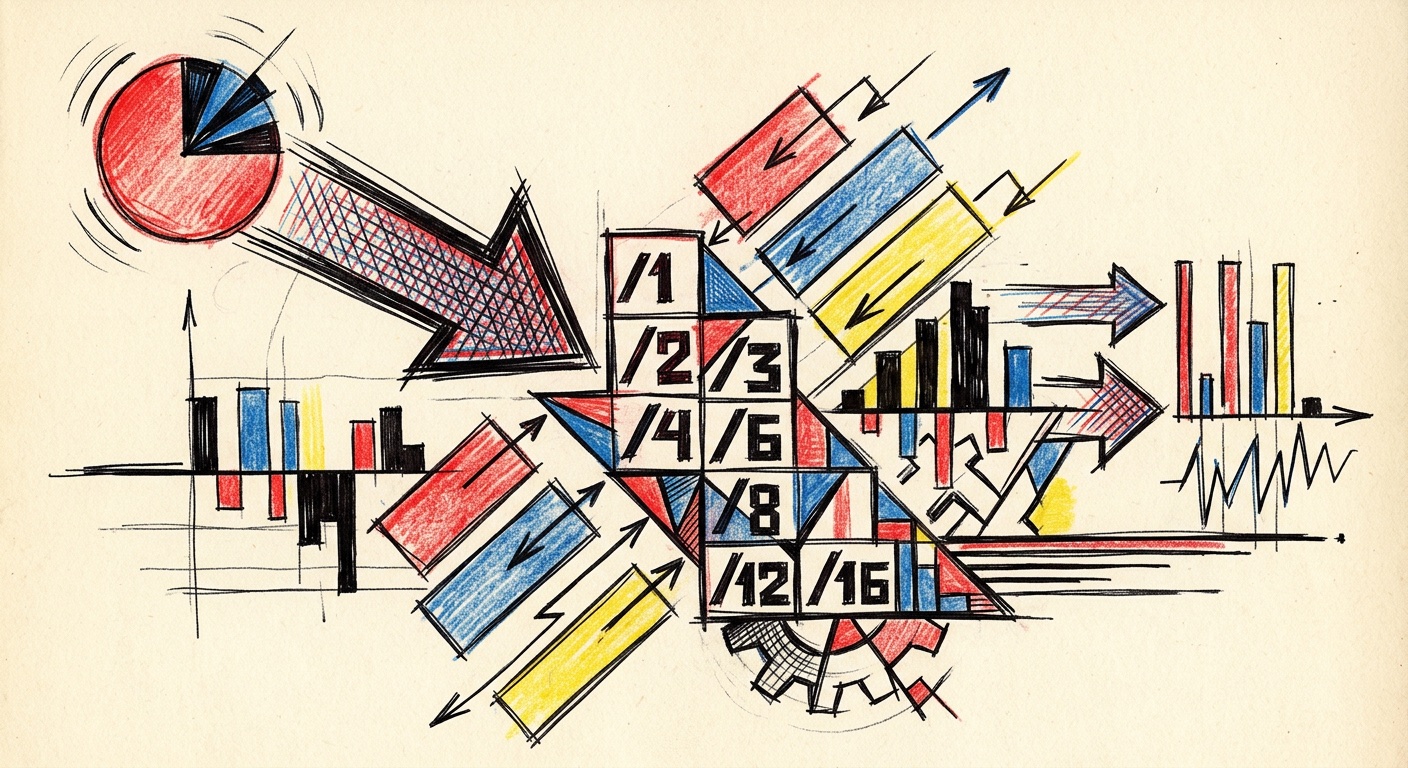

Clock division CV controls the divisor factor of a clock division or multiplication. A voltage is mapped to an integer divisor (e.g., 0V = /1, 1V = /2, 2V = /4, etc.). Similar to model select, but specifically for rhythmic division ratios.

Use Cases

- Control clock divider via CV (polyrhythmic patterns)

- Clock multiplication via CV

- Rhythmic variation in generative music

Hardware Implementation

Standard Input Stage: OpAmp → Mux → ADC

Identical to model/algorithm select.

Firmware Requirements

- Quantization via look-up table (LUT): Divisors are rarely distributed linearly in a musical context. A LUT maps the 0–5V range evenly onto musically meaningful divider arrays (e.g., /1, /2, /3, /4, /6, /8, /12, /16). Direct linear division of the ADC value yields unmusical gradations.

- Hysteresis: Identical to model select (±1/4 step width as dead zone)

- Timing: Divisor change is applied to the divider counter only on the next rising edge of the main clock (prevents "swallowed" beats)