CV Input Signal Types #4 — Reset and Run

| Property | Value |

|---|---|

| Category | Logical / Time-Based |

| Voltage Range | 0..+5V (tolerant up to +12V) |

| Polarity | Unipolar |

| Bandwidth | Single pulse (Reset) or Gate (Run) |

| Threshold | ~0.7V–2.0V |

Description

Reset and Run are control signals for sequencers and cyclic processes (LFOs, envelopes in loop mode).

- Reset is typically a trigger that returns the process to its initial state.

- Run is a gate that starts (high) or stops (low) the process.

Two standards in Eurorack:

- Run gate (Doepfer standard): High = playing, Low = paused

- Start/stop trigger (DIN-Sync derived): Separate short pulses for start and stop

Use Cases

- Reset: Return sequencer to step 1, set LFO phase to 0°

- Run: Start/stop sequencer, transport control

Eurorack Examples (Mutable Instruments)

- Marbles: Reset trigger resets internal sequence

- Stages: Reset to first segment

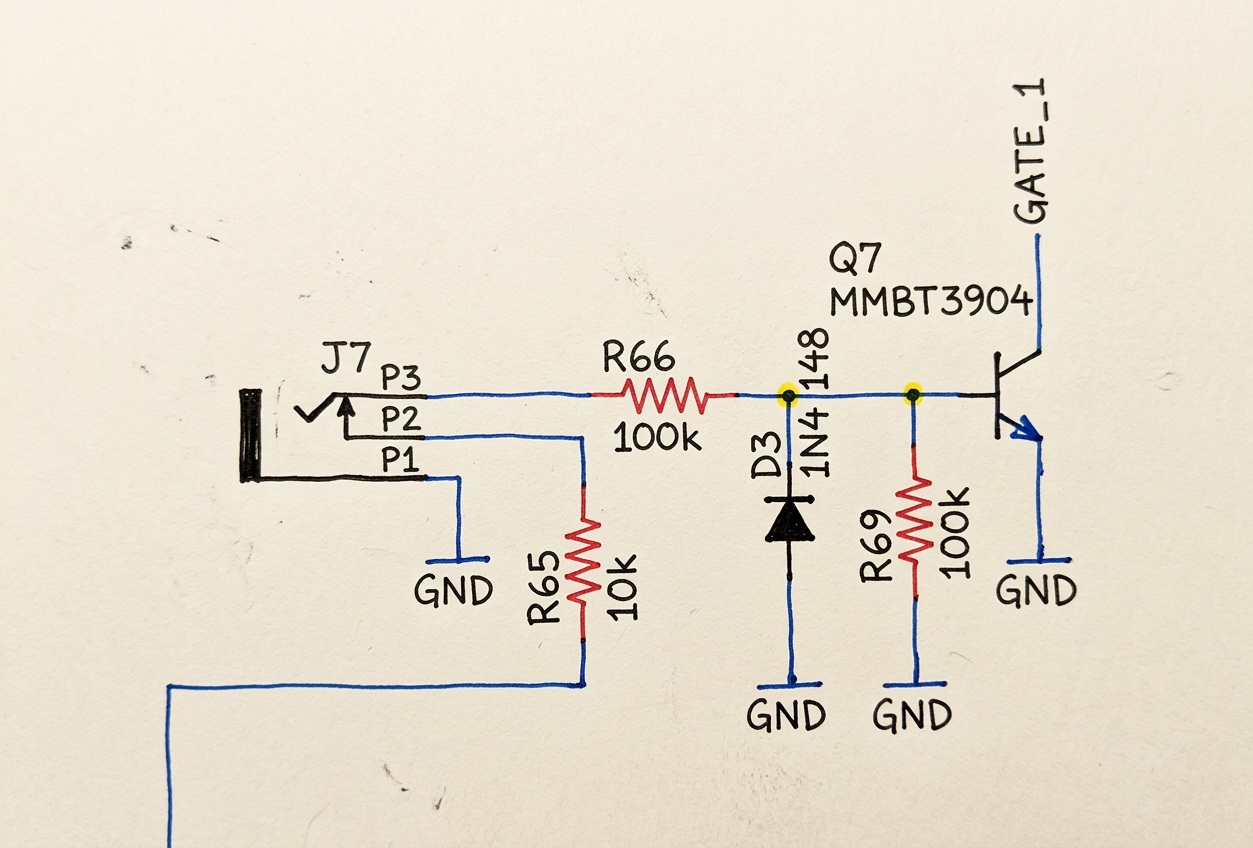

Hardware Implementation

Identical to trigger (reset) and gate (run). Same GPIO circuitry with NPN or BAT54S.

Firmware Requirements

- Reset: EXTI on rising edge, resets internal state (sequencer index = 0, LFO phase = 0)

- Run: Polling or EXTI on both edges, controls whether the process is active

Clock/Reset Race Condition (critical!)

The problem: Many master modules (e.g., Pamela's New Workout) send clock and reset at the exact same moment. If the clock interrupt is processed before the reset interrupt, the sequencer jumps to step 2 before reset sets it back to step 1 — or vice versa: reset sets step 1, the simultaneous clock immediately jumps to step 2, and step 1 is skipped.

Solution — priority logic:

- Lockout window: When reset goes high, ignore all incoming clocks for 1–2ms.

- Block-based processing: Don't blindly process clock pulses immediately — check in the same processing block whether a reset also arrived. Reset always takes priority.

- Recommended semantics: "Arm reset, and the next (or simultaneous) clock triggers step 1."